목차

1. LPCVD(Low Pressure CVD)

2. PECVD(Plasma Enhanced CVD)

3. ALD(Atomic Layer Deposition)

4. 기업요약

증착 : 웨이퍼 위에 화학 물질을 쌓아 올리는 공정

step1 : Si(규소, 모래)를 소시지처럼 길게 뽑아서 얇게 자르면 동전모양의 웨이퍼가 됨

step2 : 실리콘층은 또 p형과 n형으로 전자가 흐르는데 다른곳으로 못 움직이게 절연층(SiO2)를 얇게 덮음

step3 : 게이트층은 특정 전압을 가할 경우 실리콘층의 전류가 흐를 수 있도록 하는 역할

step4 : 각 단계를 증착하고 깍아내기(식각) 위해 빛에 반응하는 PR을 증착

step5 : 노광

step6 : 현상

step7 :식각

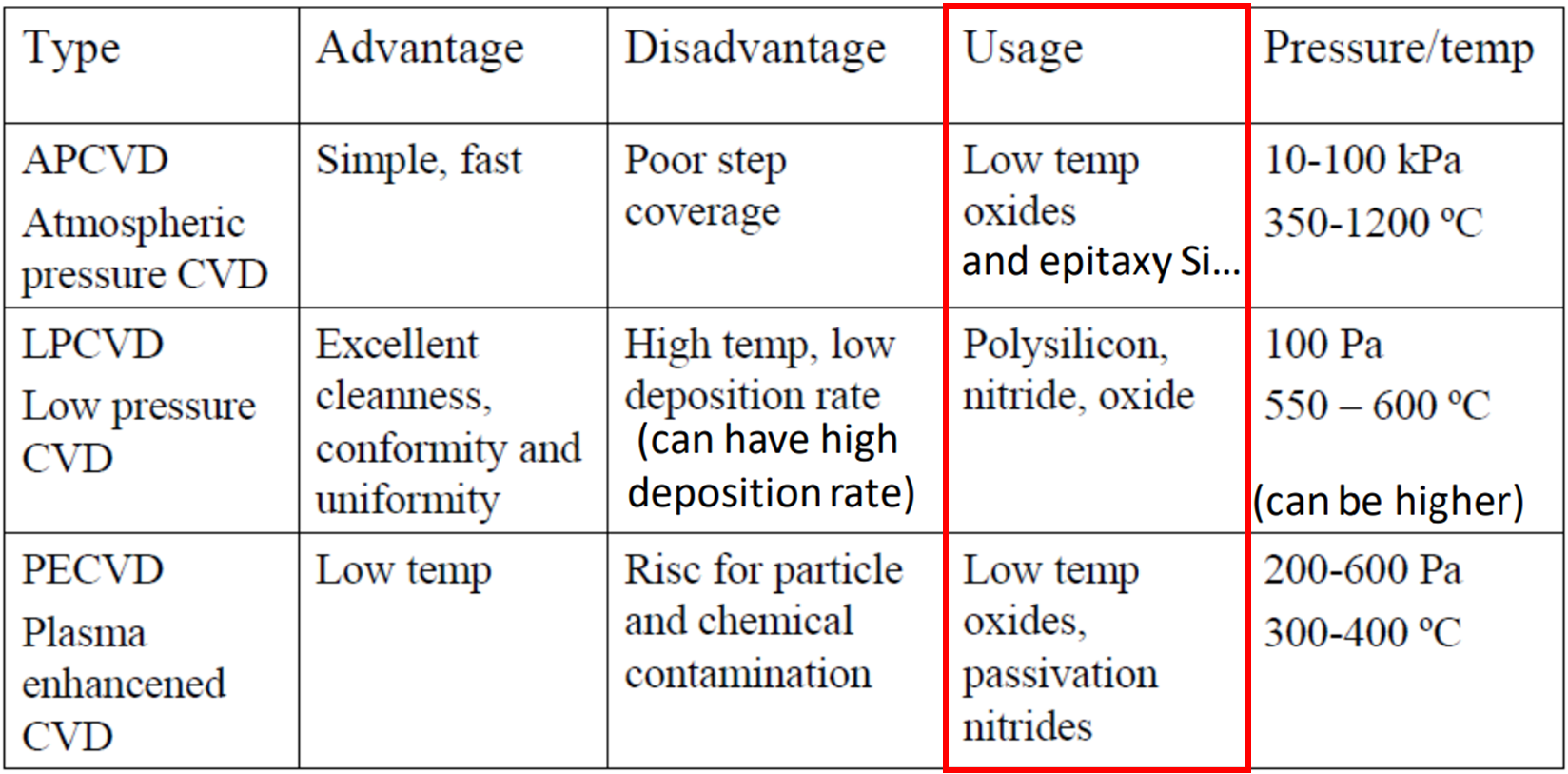

증착은 물리적(PVD, Physical Vapor Deposition)증착과 화학적(CVD)증착이 있다. PVD는 잘 안쓰이므로 생략.

1. LPCVD(Low Pressure CVD)

- APCVD(Atmospheric Pressure,대기압)에 비해 LPCVD는 챔버 내 기압을 100분의 1로 낮출 수 있음.

- 저압방식이 진행되면 진공도가 높아지고 가스 분자들끼리의 충돌이 적어짐. 이는 기체 확산도 증가하고 더 정밀하고 균일한 필름을 만들 수 있음

- 저압상태로 갈수록 공정 시간이 길어지기 때문에 온도를 높이는 과정이 필요함.

- 문제는 반도체 집적도가 증가하면서 온도 증가에 영향을 받는 막들이 생겨남.

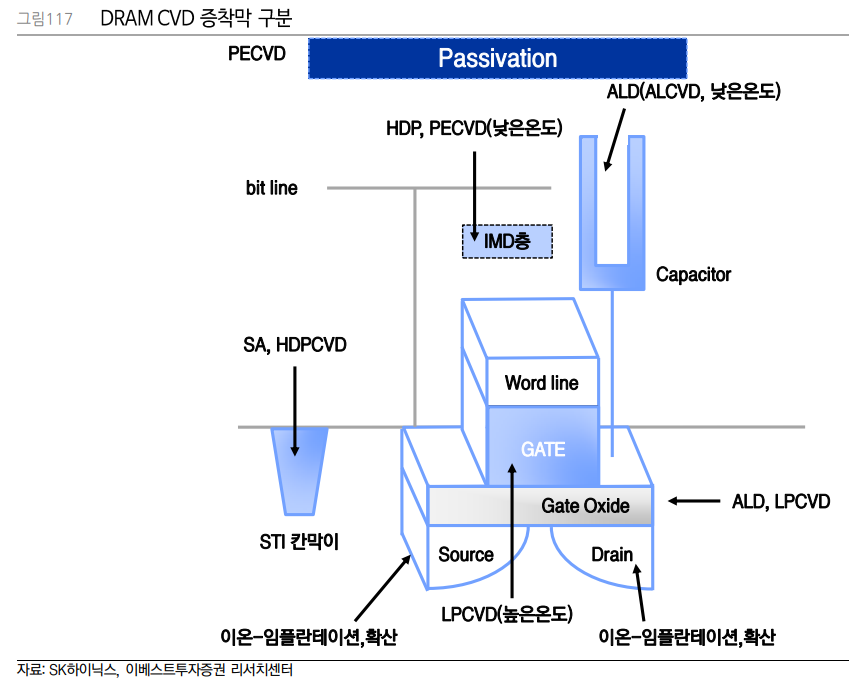

- 밑에 그림과 같이 Poly Gate, Gate Oxide 절연막 같은 하부층에 있는 막은 이상이 없으나,

- IMD(Inter Metal Dielectrics)층과 같은 트랜지스터 상부층에 위치한 막의 경우 Word line이 녹아 내리는 현상이 발생.

- 이에 따라 PECVD 장비가 개발(열 대신 플라즈마, 400도 저온)

- 사용처 : poly-Si, silicon nitride, high-temperature oxide, tungsten, WSi2

2. PECVD(Plasma Enhanced CVD)

- LPCVD의 단점을 보완하기 위해 저온(450도 이하)에서 증착하기 위함.

- 증착률(deposition rate)이 높은 것이 장점이나, 그에 따라 step coverage가 좋지 않음

* step coverage : 증착률이 높기 때문에 두께가 균일하지 않음.

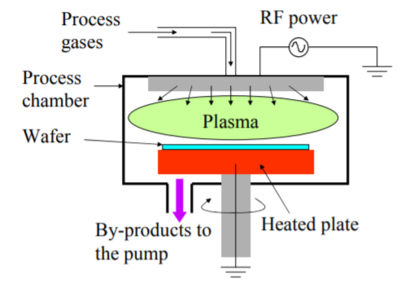

- (PECVD 원리) 반응 시킬 기체를 주입하고, 높은 전압을 수직으로 걸어주면 프라즈마 상태로 이온화된 기체들이 서로 화학 반응을 하여 원하는 물질은 기판에 쌓이게 됨.

- (속도) LPCVD는 wafer를 여러장을 옆으로 새로로 여러장 배치하였으나, PECVD의 경우 아래 사진과 같이 1장씩 배치함. 이에 따라 공정속도가 느림.

- 좋은 퀄리티의 박막을 증착할때는 PECVD를 쓰지 않음. 박막을 두껍게, 빠르게 하기 위해 사용됨. → passive nitride(소자와 공기간 차단 역할)층, 낮은 온도 이므로 메탈 위에 증착할 때 사용

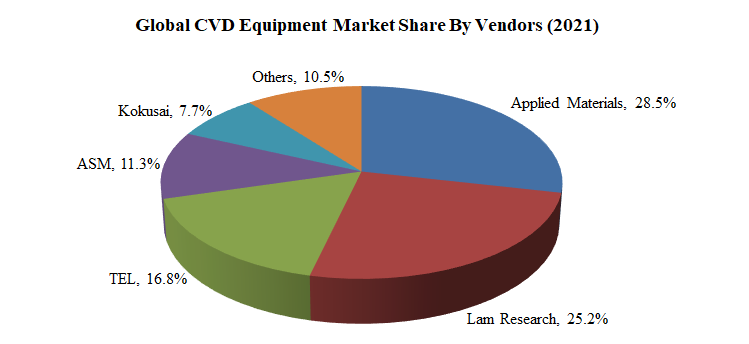

- CVD 시장

- AMAT(미), 램리서치(미), tel(일), ASM(네), 고쿠사이(일)

3. ALD(Atomic Layer Deposition)

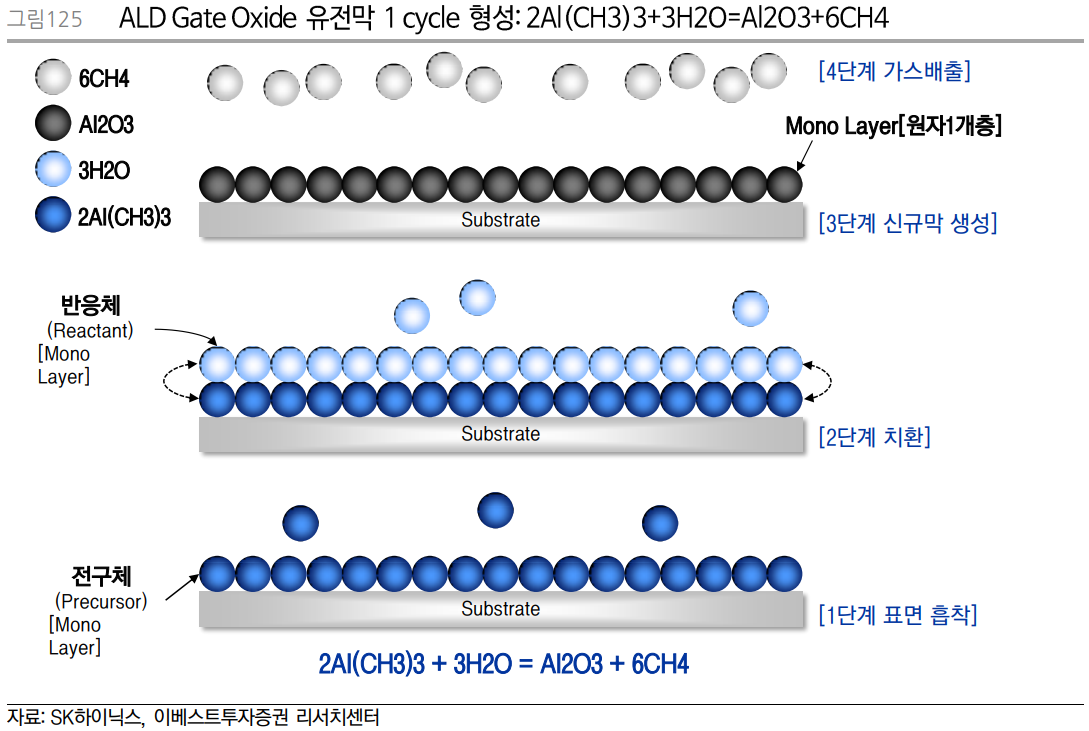

- ALD는 기본적으로 전구체 물질과 특정 반응 물질(Reactant)을 번갈아가면서 반복 주입해 웨이퍼 ‘표면’에서만 화학반응 이 일어나도록 유도하는 공법

- CVD는 챔버 안의 진공 공간과 웨이퍼 표면 모두에 화학 반응이 일어나 막이 쌓이지만, ALD는 표면에서만 반응이 일어나기 때문에 막 두께를 절반으로 구현 가능

- (장점)1cycle에는 1개층, 0.1nm, 미세 컨트롤 가능, step coverage가 좋음

- (단점)속도가 너무 느림, 전구체 선택이 어려움

- 단점을 극복하고자 batch type(wafer 여러장), spatial type(움직이며)이 개발중

- 위 그림과 같이 첫 번째 전구체 2Al(CH3)3를 substrate(wafer)위에 배치한다. 그리고 공중에 떠다니는 입자들은 purge를 이용해서 빨아들인다.

- 두 번째 전구체 3H2O를 흘려 보내면 Al2O3의 원차층이 쌓이고 나머지 반응된 6CH4는 역시 purge를 이용해서 흘려보낸다.

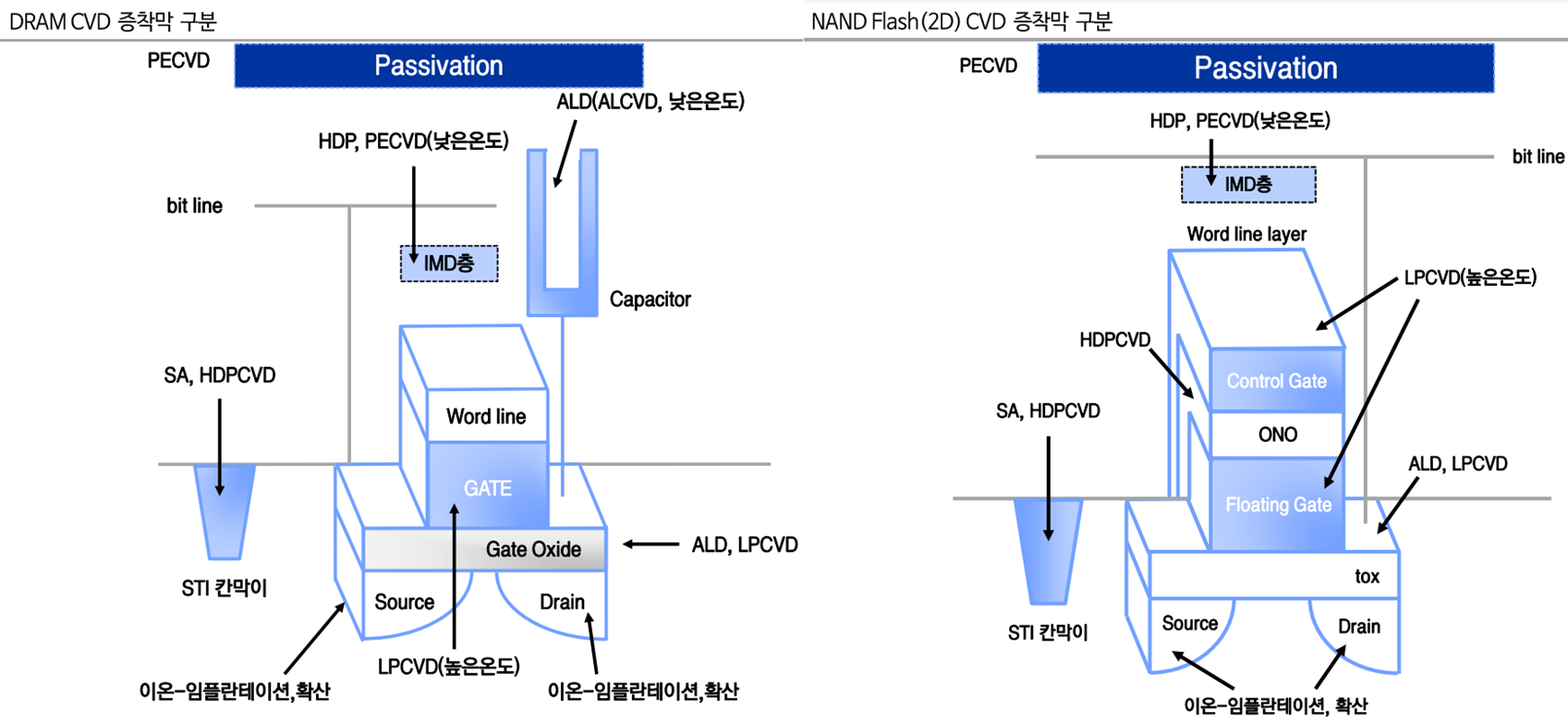

ㅇ사용처(위 그림 참조)

(1) DRAM Capacitor 형성

(2) DRAM 및 Logic에서 Gate Oxide 증착

(3) 3D NAND에서 칩 가장 아랫단까지 텅스텐 증착

(4) 선폭이 좁아지면서 간섭 현상을 줄이기 위해 커패시터 위로 하이-K 물질을 원자 단위 두께로 얇게 증착할 때 ALD 쓰임

(5) 커패시터에는 지르코늄(Zr)이나 하프늄(Hf) 같은 하이-K 물질 외 타이타늄(Ti)을 이용한 타이타늄나이트라이드(Tin) 막도 형성해야 함

(6) 실리콘나이트라이드(Si3N4) 층간 절연막을 형성하는 ILD(Inter Layer Dielectric) 공정에도 ALD가 활용

ㅇ기업

- LPCVD : AMAT, TEL, Hitachi, 원익IPS, 국제일렉트릭, 유진테크, 주성엔지니어링

- PECVD : AMAT, Lam Research, TEL, 원익IPS, 테스, 주성엔지니어링, 세메스

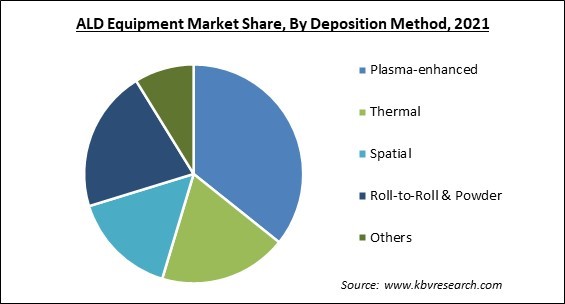

- ALD(single) : ASML(40%), 램리서치(27%), 원익IPS(12%), 주성엔지니어링(12%), 유진테크(3%)

- ALD(Batch) : 고쿠사이(80장씩) 유진테크(150장씩)

- ALD(mini Batch) :

4. 기업 정리(원익IPS, 주성엔지니어링, 유진테크, 테스)

가. 원익IPS

(1) 매출구성 : 반도체(75%), 디스플레이(25%), 시가총액(1조 5167억, '23.8.24기준)

(2) GEMINI(PE-CVD)

- 반사막 및 하드마스크와 같은 유전막 필름을 형성하는데 사용되며, 20nm이하 DRAM공정에서 더블 및 쿼드로플 패터닝 하드마스크 용도로 사용

- 삼성전자 3nm 파운드리 GAA공정에 GEMINI 설비를 활용한 PE-CVD방식의 공정과 멀티패터닝 기술이 적용되어 진입해 있는 상황

(3) WIDAS(열처리장비)

- 패치당 175장, 스텝커버리지(95%이상)

- 100~400도(구리 어닐링과 합금), 400~1000도(열산화, 플로우 공정), 1000도 이상(고밀화, 웰 드라이브인 공정)

- 3D NAND 분야의 핵심 증착 장비(CUARTO, CLARO, NOA 등)

- DRAM 분야의 핵심 증착 장비(HYETA, GEMINI, PRESTO 등) 및 Foundry 분야의 핵심 증착 장비(GEMINI, PRESTO 등)를 개발 및 양산화를 추진하여 차세대 시장 진입에 성공하였습니다.

당사 열처리 장비의 경우 100°C~1,350°C 온도 영역대에서 최첨단 반도체 양산라인에서 요구되는 높은 성숙도의 다양한 열처리 공

(4) 뉴스요약

- 21년 초 : 원익IPS는 텅스텐을 올리는 일반 증착 장비 4대 정도를 SK하이닉스로부터 수주

- 21.4월 : 하이닉스에서 주성의 high-K ALD 장비는 30여대 수주(원래 주성이 100% 납품 하다가 원익과 나누어 납품함. 이번에 원익의 장비가 문제가 생겨 다시 주성이 100% 납품)

(5) 현재 상황

- ALD상용화가 더디어 주가 부진

- 3나노GAA 14나노 D램 등의 수혜 기대

나. 주성엔지니어링

(1) 매출구성 : 23년2분기 기준 반도체 : 디플 = 96:4, (중국 매출 비중 48%), 시가총액(1조 3100억, '23.8.24. 기준)

(2) 제품

SPD-CVD : 공간 분할 플라즈마 CVD장비이며 D램, 하이k에 적용

주성이 이번에 공개하는 TSD 시스템은 열(Thermal) 원자층증착(ALD), 플라즈마(PE) 원자층증착, IPT(In Cycle Plasma Treatment) 등을 하나의 하드웨어에서 모두 구현할 수 있는 장비

(3)뉴스요약

- 19.5월 : 0.5세대 대형 OLED 라인용 TFT 증착장비 1대를 발주(200억)

- 19.6월 : LG디플에서 10.5세대 AML 장비 2대, 주성 장비 1대 계약(과거 8세대는 주성5대, AML 4대)

- 21.4월 : 하이닉스에서 주성의 하이-K ALD 장비는 30여대 수주(원래 주성이 100% 납품 하다가 원익과 나누어 납품함. 이번에 원익의 장비가 문제가 생겨 다시 주성이 100% 납품)

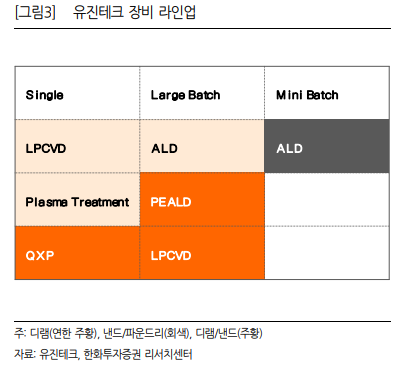

다. 유진테크

(1) 시가총액 : 7780억('23.8.24.기준)

(2) 제품

- 화학기상증착(CVD) 장비 대당 가격이 30~40억원이라면 ALD 퍼니스 장비 가격은 60~70억원

- 삼성 평택 D램 신공장에 13대 납품

- 삼성에 납품하는 유진테크의 ALD공정은 실리콘나이트라이드(Si3N4) , TEL의 ALD는 타이타늄나이트라이드(TiN)

- D램의 커패시터 전극막 형성을 위 TiN증착을 위한 ALD는 개발중('22년 3월) → 특허 등 완료('23년 5월)

- 2022년까지 SK하이닉스의 매출 비중이 6~70% 차지하였으나, 이번 Batch type 납품으로 공급사 다변화

(3) 뉴스 요약

- 16.08.03. 삼전 : 하닉 = 54:46, 삼전은 3D NAND의 플라즈마 treatment, 하닉은 M14 DRAM 공정 전

- 16.11.18. : single type 납품으로 batch보다 생산성이 낮으나, 높은 균일성으로 기술 인정

- 17.05.26. : 엑시트론의 AVD, CVD 사업부문 인수 발표

- 19.04.11. : '18년에는 DRAM : NAND = 96 : 4

- 20.07.06. : 퀄 테스트 - 1)DRAM Large Batch Thermal ALD, 2) 비메모리향 mini batch Thermal ALD, 3) NAND향 Metal QXP)

- 21년 4월 : 삼성전자에서 고쿠사이에서 납품받던 ALD장비를 유진테크에서도 수주함.

- 23.02.09. : 삼전향 매출 50% 넘음, 1b, 1c 선행공정에서 담당 레이어수 추가 확대 시행

- 23.04.04. : 삼전향 매출 90% 넘음(삼전 확대, 하이닉스 축소)

- 23.08.07. : 하이닉스 투자 축소, 삼전 '23.3Q투자 없을 예

라. 테스

(1) 매출구성 : 내수 79%, NAND : DRAM = 6 : 3, (시가총액 3964억, '23.8.24 기준)

(2) 제품

- ACL PECVD : 비정질탄소층(Amorphous Carbon Layer) 3D NAND에서 활용 높음(18년 양산)

- BSD PECVD : wafer Warpage현상을 방지하기 위한 막 형성(22년 양산)

램리서치가 독점해오돈 BSD장비를 국산화에 성공,

- Low-K PECVD: Low-K물질 증착(22년 양산)

- a-Si PECVD : 비결절실리콘(amorphous silicon Hard Mask 증착(21년 양산)

- Dry Clean: 플라즈마를 이용한 radical etch장비(22년 양산)

- GPE(Gas Phase Etching) :식각 후 파티클 세정장비이며 HF(불화수소)가스를 사용해 웨이퍼 표면의 산화막 선택적 제거

플라즈마 사용 식각

-ARC 장비는 노광공정에서 발생할 수 있는 난반사를 방지하기 위함. DRAM향 비중이 상대적으로 높음

(3) 기타

- 매출 중 삼성전자의 NAND 제조 장비 비중이 제일 높음. 이는 하드마스크 증착장비가 3D NAND의 핵심 공정인 홀 에칭에 적용

🔍 식각 파츠(Ring, Electrode, Si/SiC), 시장, 업체별 정리(티씨케이, 하나머티리얼즈, 월덱스, 케이엔제이)

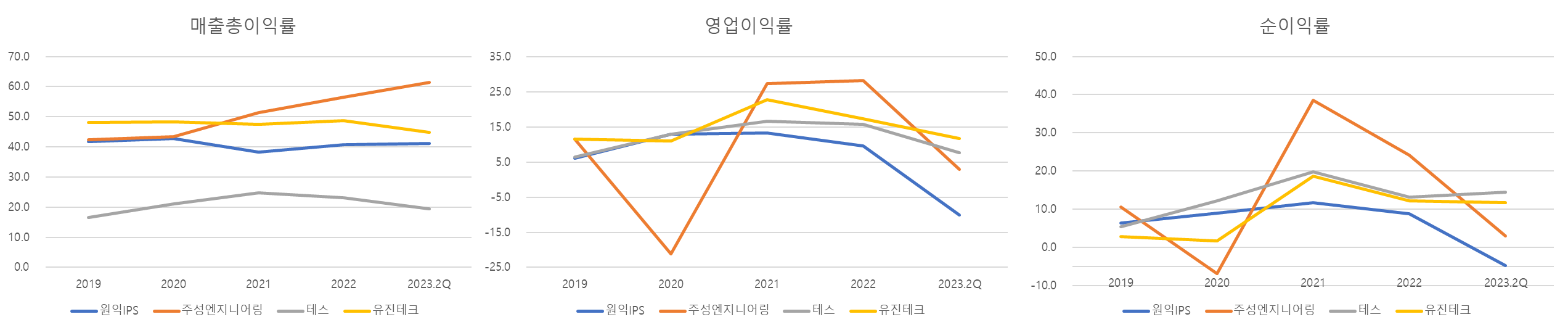

5. 연도별, 기업별 매출이익률, 영업이익률, 순이익률

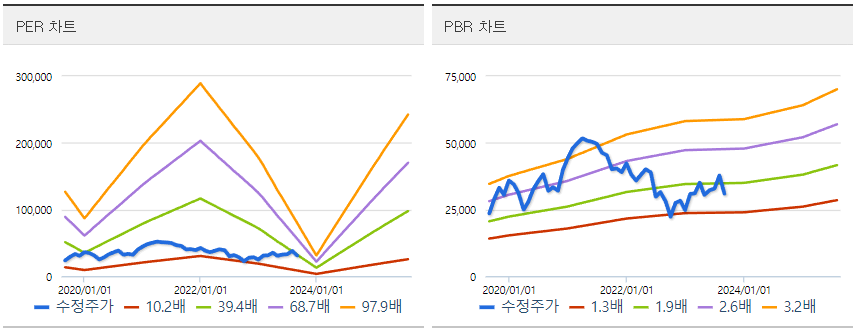

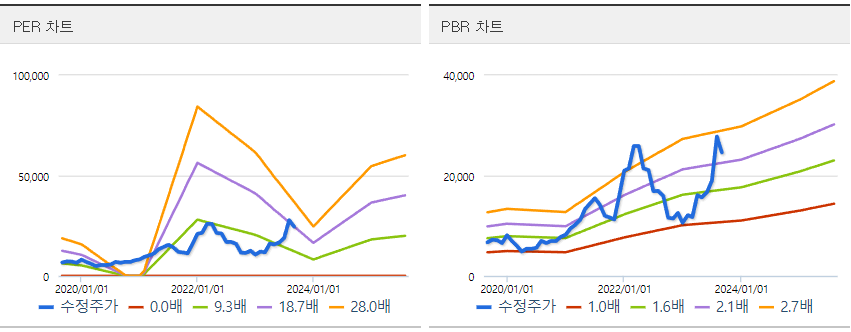

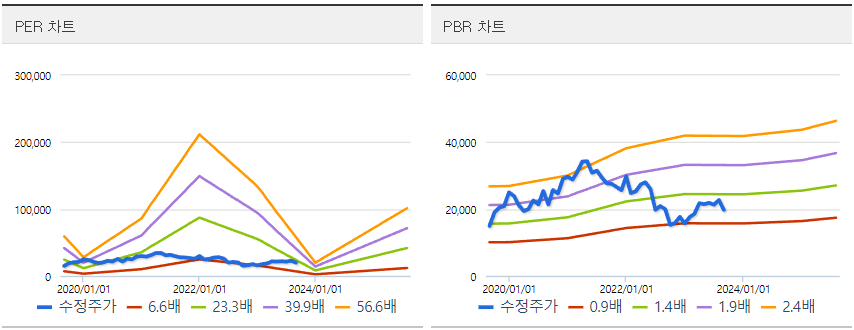

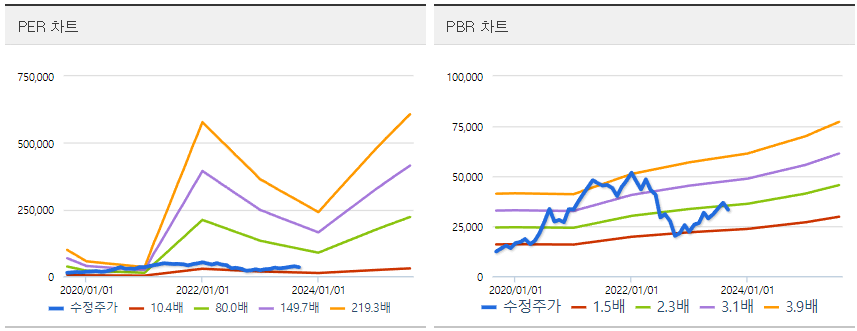

ㅇ PER, PBR밴드 차트(2023.8.24.기준)

🔍 식각의 모든 것(원리, 장비, 산업, 시장, 기업)

📖 함께 보면 좋은 글

🔍 경기 둔화에 따른 매수 섹터 분야(f.미국 ETF섹터)

🔍 트럼프 2기와 달러 패권 – 글로벌 경제의 힘의 균형 변화

🔍 에너지 패권이 흔드는 세계 경제 – 2025년 글로벌 질서의 변화🌍

🔍 🤖 2편: AI 로봇이 극복해야 할 기술적 난제 5가지

'주식' 카테고리의 다른 글

| 넥스틴 기업분석(패턴 결함 검사) 및 경쟁기업 (0) | 2023.08.29 |

|---|---|

| 식각 파츠(Ring, Electrode, Si/SiC), 시장, 업체별 정리(티씨케이, 하나머티리얼즈, 월덱스, 케이엔제이) (0) | 2023.08.25 |

| 식각의 모든 것(원리, 장비, 산업, 시장, 기업) (0) | 2023.08.20 |

| 주식분석(2), 퀀트에서 상관관계 분석(heatmap) (0) | 2023.07.06 |

| 주식분석(1), 퀀트와 머신러닝(랜덤포레스트)을 이용 (0) | 2023.07.04 |